**Data Sheet**

## 1 Product Overview

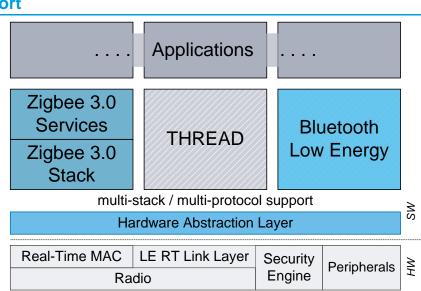

The QPG6105 is a multi-standard Smart Home communications controller supporting Zigbee, Thread, Matter™, Bluetooth® Low Energy and Bluetooth® Mesh, enabling greater interoperability and scalability.

It features ConcurrentConnect<sup>™</sup> technology enabling multiple protocols to operate simultaneously, delivering improved capacity and enhanced interoperability with the leading low power standards.

- ConcurrentConnect Multi-Radio capability allows continuously scanning for incoming packets across

Bluetooth Low Energy and IEEE 802.15.4 protocols with no observable blind spots.

- Patented ConcurrentConnect Antenna Diversity enables increased effective range.

- ConcurrentConnect Multi-Channel capability allows operating in up to 3 PANs on different channels.

- Simplify Gateway dependencies by bridging Zigbee, Thread and/or Bluetooth Mesh networks.

- Enhanced security capabilities enable highly secure solution with built in support for secure boot, secure OTA software upgrade and secure identity.

- Optimized connected lighting design BOM, reducing the number of components and PCBs in the design.

- Qorvo's turn-key development kits include complete software applications and hardware designs; enabling quick development of Connected Lighting and Smart Home products.

- Designed for low power IoT end node applications such as:

- o Connected Lighting o Sensors o Smart Plugs o Thermostats o Wearables

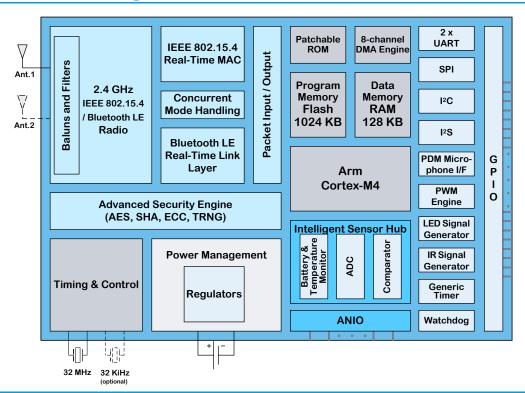

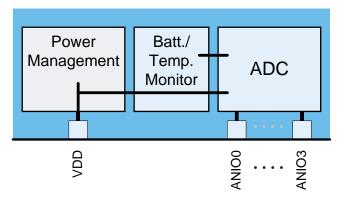

# 2 Functional Block Diagram

# 3 Key Features

#### Radio

- ✓ Operates in the worldwide 2.4 GHz ISM-band

- ✓ Integrated baluns and RF filters

- ✓ In 1 dB steps, programmable transmitter output power up to +10 dBm

- Targeting compliance with worldwide RF regulations: ETSI EN 300 328 (Europe), FCC CFR47 Part 15 (US), and ARIB STD-T-66 (Japan)

### IEEE 802.15.4 compliant PHY and Real-Time MAC

- Preamble-based ConcurrentConnect Antenna Diversity

- ✓ Packet-in-Packet resynchronization

- ConcurrentConnect Multi-Channel capability, operating in up to 3 PANs on different channels

## Bluetooth v 5.3 compliant Low Energy Controller

- ✓ Enhanced Data Rate (2 Mbits/s)

- ✓ Link Layer Privacy and Advertising Extensions

- ✓ Full connection utilization

#### **Multi-Stack Support**

- ✓ Multiple IEEE 802.15.4 based stacks MAC API

- ✓ Bluetooth Low Energy HCI

#### **Dynamic Multi-Protocol**

- Hardware accelerated Dynamic Multi-Protocol Bluetooth Low Energy and IEEE 802.15.4 communications

- → Allows combining Bluetooth Low Energy Peripheral with any type of Zigbee/Matter-over-Thread device

## ConcurrentConnect Multi-Radio capability

- ✓ Concurrent IEEE 802.15.4 and Bluetooth listening

- → Allows combining Bluetooth Low Energy Central/Observer or Mesh Node with Zigbee/Matter-over-Thread router

#### **Advanced Security Engine**

- Hardware accelerated AES and CCM/CCM\* encryption and decryption with 128, 192 and 256bit keys

- ✓ Hashing engine: SHA-128, SHA-2 (SHA-256, SHA-512)

- ✓ Public Key Crypto: Elliptic Curve; support for ECDSA, ECDH, P256, Curve25519, J-Pake, ECMQV, EdDSA, etc.

- ✓ Cryptographic Random Number Generator

#### **Built-in Security Features**

- ✓ Secure boot

- ✓ Secure OTA software upgrades

- ✓ Secure identity

#### **Integrated Microcontroller**

- Arm® Cortex®-M4 processor with DSP functionality

- Up to 64 MHz clock speed

#### Memory

- √ 1 Mbyte Flash Program memory

- ✓ Patchable ROM for Flash offload

- √ 128 Kbyte Low Leakage Retention RAM

- √ 8-Channel DMA Engine

## **Peripherals and Interfaces**

- ✓ Up to 23 Programmable GPIO lines

- Up to 4 Analog input lines

- Full internal IO pull-up / pull-down support during active and standby states

- ✓ Two UART interfaces

- ✓ SPI Master and Slave interfaces

- √ I<sup>2</sup>C Master and Slave interfaces

- √ I²S Master/Slave interface for digital audio devices

- ✓ PDM Microphone Interface

- ✓ PWM Engine (16-bit PWM ) for 8 outputs

- ✓ LED Signal Generator (8-bit PWM) with fading support for 4 signaling LEDs

- ✓ IR Signal Generator

- √ 10/12-bit ADC to monitor the ANIO pins, the power supply level and the temperature

- ✓ Low power comparator

#### **Power Management**

- ✓ Operating voltage range: 1.8 ... 3.6V

- Integrated Regulators

- ✓ Low power standby modes:

Using internal LjRC oscillator:  $0.9 \mu A$  Using 32 MHz crystal oscillator:  $765 \mu A$  Using 32 KiHz crystal oscillator:  $1.6 \mu A$

✓ Data and state retention in all standby modes

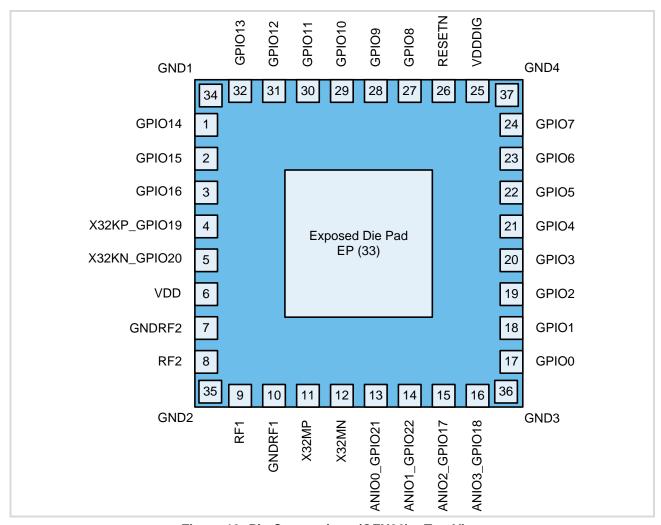

#### **Dimensions and Layout**

- ✓ QFN32, 4x4 mm package (0.4 mm pitch)

- ✓ Supports direct interfacing with printed antennas

- ✓ No RF shielding required

#### **Environmental Aspects**

✓ RoHS compliant

# **4 Ordering Information**

| Part Number | Chip<br>Package | Flash    | RAM       | Packing           | Unit Quantity (number of chips) | Box<br>Dimensions |

|-------------|-----------------|----------|-----------|-------------------|---------------------------------|-------------------|

| QPG6105TR13 | QFN32           | 1 Mbyte  | 128 Kbyte | 13" Tape and Reel | 4500                            | 37 x 35 x 8 cm    |

| QPG6105SR   | QIIIOZ          | 1 Wibyte | 120 Rbyto | 7" Tape and Reel  | 100                             |                   |

# **Table of Contents**

| l | Produc         | ct Overview                                           | 1  |

|---|----------------|-------------------------------------------------------|----|

| 2 | Function       | onal Block Diagram                                    | 1  |

| 3 | Key Fe         | eatures                                               | 2  |

| 1 | •              | ng Information                                        |    |

| 5 |                | onal Description                                      |    |

| • |                | 4 GHz Radio                                           |    |

|   | 5.1.1          | RF Ports with Integrated Switch, Matching and Filters | 5  |

|   | 5.1.2          | Radio Configurations                                  | 5  |

|   | 5.1.3          | RSSI                                                  |    |

|   | 5.1.4          | Transmit Power Control                                | .6 |

|   |                | EE 802.15.4 Communications                            | 6  |

|   | 5.2.1          | 2.4 GHz IEEE 802.15.4 Transceiver                     | 6  |

|   | 5.2.2          | ConcurrentConnect™ Antenna Diversity                  |    |

|   | 5.2.3          | Clear Channel Assessment (CCA)                        | 6  |

|   | 5.2.4          | Packet-in-Packet Resynchronization                    | 6  |

|   | 5.2.5          | Real-Time Medium Access Control (MAC)                 | /  |

|   | 5.2.6<br>5.2.7 | Link Quality Indication                               | /  |

|   |                | uetooth Communications                                |    |

|   | 5.3.1          | 2.4 GHz Bluetooth Low Energy PHY Layer                |    |

|   | 5.3.2          | Real-Time Bluetooth Low Energy Link Layer             |    |

|   | 5.3.3          | Full Connection Utilization                           |    |

|   |                | ulti-Stack Support                                    |    |

|   |                | W-Accelerated Dynamic Multi-Protocol Support          |    |

|   |                | oncurrentConnect™ Multi-Radio Capability              |    |

|   | 5.7 Ad         | dvanced Security Engine                               | 8  |

|   |                | uilt-in Security Features                             |    |

|   |                | acket Input Output (PIO)                              |    |

|   |                | emory Architecture                                    |    |

|   |                | ternal Microcontroller                                |    |

|   |                | eripherals                                            |    |

|   |                | IO Pins                                               |    |

|   |                | UARTsSPI Master                                       |    |

|   |                | SPI Slave                                             |    |

|   |                | I <sup>2</sup> C Master                               |    |

|   |                | I <sup>2</sup> C Slave                                |    |

|   |                | I <sup>2</sup> S Master/Slave                         |    |

|   |                | IR Signal Generator                                   |    |

|   |                | LED Signal Generator                                  |    |

|   |                | OPDM Microphone Interface                             |    |

|   |                | 1 PWM Engine                                          |    |

|   |                | 2 Generic Timer                                       |    |

|   |                |                                                       |    |

| 5.12.13 Watchdog                                      |    |

|-------------------------------------------------------|----|

| 5.12.14 Intelligent Sensor Hub                        | 13 |

| 5.12.15 Clock Output                                  | 14 |

| 5.13 Timing and Control                               | 14 |

| 5.13.1 Oscillator Settings                            | 15 |

| 5.13.2 Standby Modes                                  |    |

| 5.14 Power Management                                 | 16 |

| 5.14.1 Low Voltage Behavior                           |    |

| S Electrical Characteristics                          |    |

| 6.1 Absolute Maximum Ratings                          |    |

| 6.2 Recommended Operating Conditions                  |    |

| 6.3 Current Consumption                               |    |

| 6.4 Receiver Characteristics                          |    |

| 6.5 Transmitter Characteristics                       |    |

| 6.6 Digital Timing Characteristics                    |    |

| 6.7 Reset, Wake up and Standby Timing Characteristics |    |

| 6.8 Flash Memory Characteristics                      |    |

| 6.9 Crystal Oscillator Specifications                 | 30 |

| 6.9.1 The 32 MHz Crystal Oscillator                   |    |

| 6.9.2 The 32 KiHz Crystal Oscillator (optional)       |    |

| 6.10 Internal Pull-up / Pull-down Characteristics     |    |

| 6.11 ADC Characteristics                              |    |

| 6.12 Battery / Temperature Monitor Characteristics    |    |

| 6.13 Comparator Characteristics                       | 33 |

| 6.14 32 kHz LjRC Oscillator Characteristics           | 33 |

| 7 Application Circuit                                 |    |

| 3 Application Programming Information                 |    |

| 8.1 Multi-Protocol Support                            |    |

| • •                                                   |    |

| 9 Flash Programming and Configuration                 |    |

| 9.1 SPI Programming Interface                         |    |

| 9.2 UART Programming Interface                        |    |

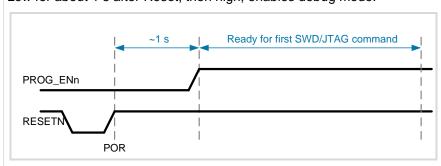

| 10 Debug Mode                                         |    |

| 11 Device Information                                 | 37 |

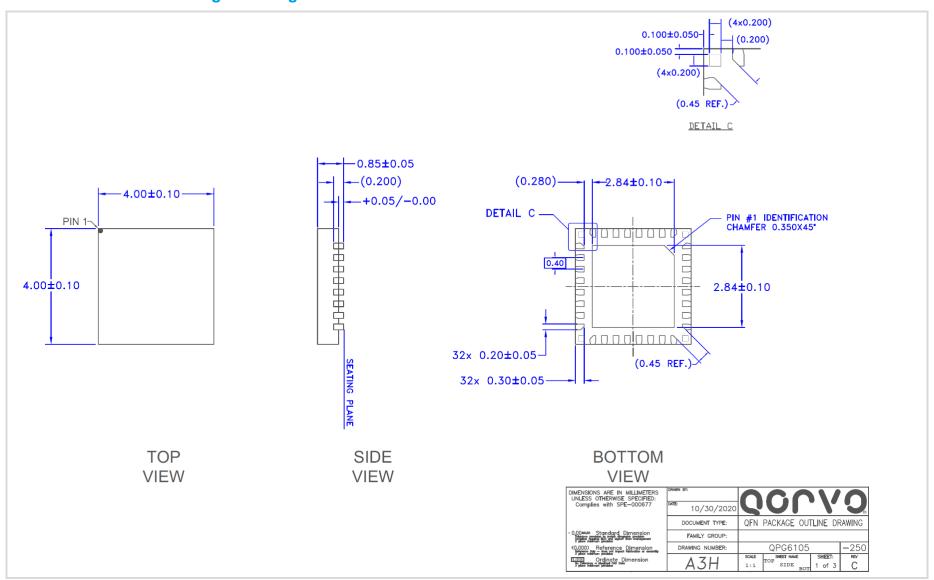

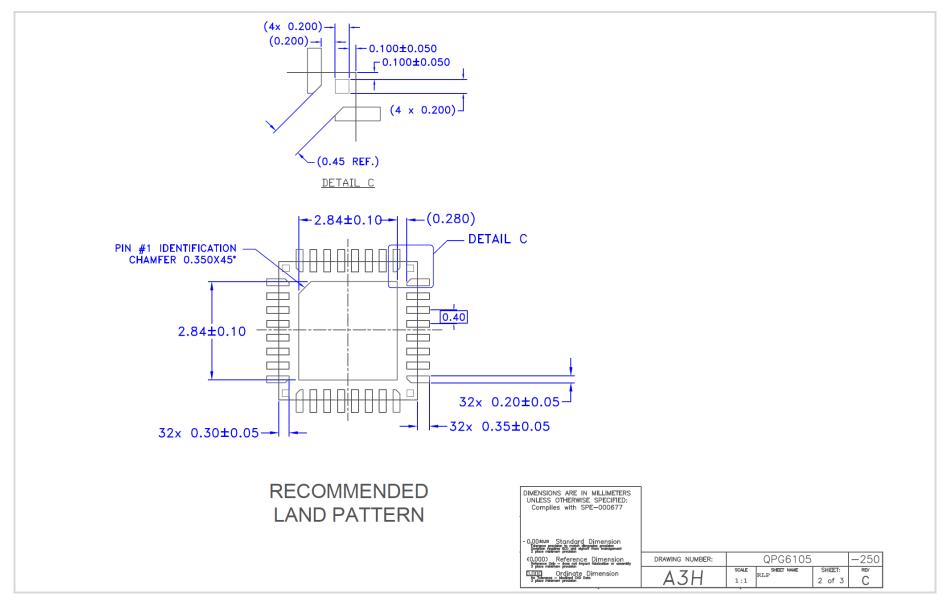

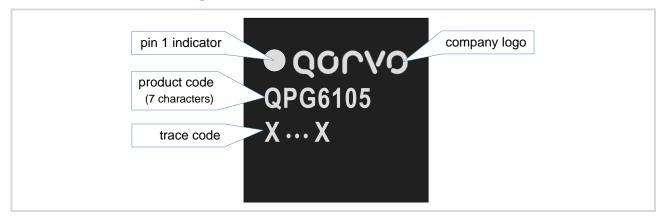

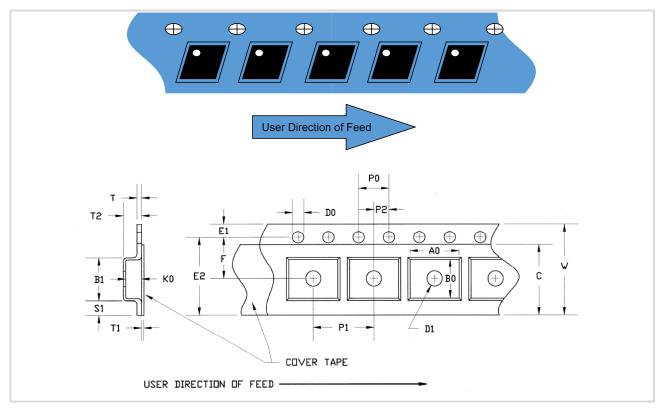

| 11.1 QFN32 Package                                    | 37 |

| 11.1.1 QFN32 Pin Assignments                          |    |

| 11.1.2 QFN32 Package Drawings                         |    |

| 11.1.3 QFN32 Package Information                      |    |

| 11.1.4 QFN32 Thermal Characteristics                  |    |

| 11.1.5 QFN32 Tape and Reel Information                |    |

| 11.2 Moisture/Reflow Sensitivity                      |    |

| 11.3 RoHS Compliance                                  | 48 |

| 12 Errata                                             | 49 |

| 12.1 Spurious External Event                          | 49 |

| Abbreviations                                         | 50 |

| mportant Notices                                      |    |

| Product Status                                        |    |

|                                                       |    |

| Document History                                      | 52 |

# **5 Functional Description**

#### 5.1 2.4 GHz Radio

The QPG6105 radio transceiver provides all the functionality for the Physical layer (PHY) for both the IEEE 802.15.4 and the Bluetooth communications.

This section describes the generic features; following sections describe the specific features for IEEE 802.15.4 and Bluetooth.

## 5.1.1 RF Ports with Integrated Switch, Matching and Filters

The QPG6105 has two antenna ports with integrated switch, matching and RF filters. The antenna ports output is  $\Omega$  single ended. Optionally the outputs can be combined to one 200  $\Omega$  differential output.

## 5.1.2 Radio Configurations

The QPG6105 supports several different radio configurations. It can be configured to use a different receive and transmit antenna, or for IEEE 802.15.4 communications it can use antenna diversity (see section 5.2.2). A few sample configurations are depicted below, but others are also possible.

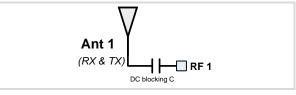

#### Sample Configuration 1 (Figure 1):

- Single ended 50 Ω antenna

- Using antenna 1 (RF1 pin) for both RX and TX

- Antenna diversity disabled

Figure 1: Single Antenna

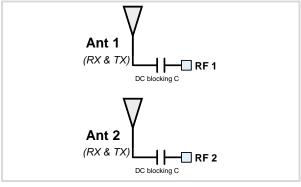

#### Sample Configuration 2 (Figure 2):

- 2 Single ended 50 Ω antennas

- TX on same antenna as was selected best by RX

- Antenna diversity enabled (for IEEE 802.15.4)

Figure 2: Two Antennas

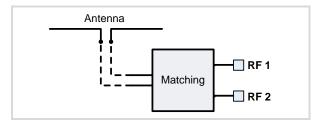

## Sample Configuration 3 (Figure 3):

- Symmetrical antenna

- Antenna diversity disabled

Figure 3: Symmetrical Antenna

## 5.1.3 **RSSI**

The PHY's RSSI circuitry measures the received signal energy level and this value is converted to dBm values in the Hardware Abstraction Layer (HAL). See Receiver Characteristics (6.4 below) for the range and accuracy.

#### 5.1.4 Transmit Power Control

The QPG6105 can be configured for two transmitter output power modes:

- Low power mode; TX output power up to 7 dBm

- High power mode; TX output power up to 10 dBm

The transmitter output power is configured by software, in steps of 1 dB.

#### 5.2 IEEE 802.15.4 Communications

#### 5.2.1 2.4 GHz IEEE 802.15.4 Transceiver

The QPG6105 radio is compliant with the IEEE 802.15.4 standard as required for supporting Zigbee and Thread.

The QPG6105 supports all the IEEE Standard 802.15.4 defined channels in the 2.4 GHz ISM license-free frequency band (channels 11 .. 26).

The channel number (k) and center frequency ( $F_c$ ) relate as follows:  $F_c = 2405 + 5(k - 11)$  in MHz

## **5.2.2** ConcurrentConnect™ Antenna Diversity

IEEE 802.15.4 Preamble based Antenna Diversity enables the PHY to choose the optimal antenna for every individual packet, and increases the performance of the receiver in environments that are dominated by multipath fading effects and interference situations. In receive mode the PHY selects the antenna based on the best signal quality (signal-to-noise/interference ratio).

For typical indoor usage in an environment with 50 ns delay-spread and 2 MHz signal bandwidth using the Rayleigh fading model, antenna diversity with 2 antennas results in a ~8 dB improved link budget (at a 1% outage probability) compared to no antenna diversity. This translates into 70% more reliable range (using a log-distance breakpoint model<sup>1</sup> with path loss coefficients g1=2 (free space propagation) and g2=3.5 above the breakpoint at 10 m).

Unless configured otherwise, the QPG6105 will use the same antenna for transmission as the one that was used for the reception of the last packet.

## 5.2.3 Clear Channel Assessment (CCA)

The PHY can perform a clear channel assessment (CCA) to avoid collisions. The IEEE 802.15.4 standard defines 3 CCA methods; the QPG6105 supports:

CCA mode 1, **Energy Detect (ED)**: The medium is considered busy when the measured energy in the selected channel is above a certain threshold. This CCA threshold is programmable.

CCA mode 3, **Energy Detect (ED) and Carrier Sense (CS)**: The medium is considered busy when a valid IEEE 802.15.4 carrier is detected in the selected channel and the measured energy in the selected channel is above the programmable threshold.

## 5.2.4 Packet-in-Packet Resynchronization

If the QPG6105 is receiving a packet from one node and is interrupted by the reception of another stronger packet from another node, the receiver will resynchronize to the latter and continue to receive and process this packet. This allows one packet (the strongest) to be received where otherwise both packets would have been lost. Packet-in-Packet collisions can occur in situations when neighbor network packets are received at a low level and in hidden node situations where not all nodes can see each other.

<sup>&</sup>lt;sup>1</sup> Refer to "T.S. Rappaport, Wireless Communications – Principles & Practice, Prentice Hall, 1996" for this model.

## 5.2.5 Real-Time Medium Access Control (MAC)

The QPG6105 implements all Zigbee and Thread-required MAC features of the IEEE Standard 802.15.4. The MAC provides a packet-level service to the protocol stack, and handles packet transmissions and receptions autonomously, including:

- Performing CSMA/CA to avoid collisions when transmitting packets;

- Adding CRC and Sequence number;

- Acknowledgement handling for transmitted packets, including automatic retransmissions;

- Option to spread retransmissions over different channels to natively support rf4ce multi-channel acknowledged transmission schemes

- Address recognition and packet filtering on received packets, including CRC checking;

- Acknowledgement handling for received packets, including automatic acknowledge transmission.

## 5.2.6 Link Quality Indication

In addition to the RSSI, there is also a link quality indication (LQI) determined for each received IEEE 802.15.4 data packet, for use at the network and application layers.

## **5.2.7** ConcurrentConnect™ Multi-Channel Capability

For the IEEE 802.15.4 communications, the QPG6105 can simultaneously listen for packets on three different PANs (Personal Area Networks) that may be on the same or on different RF channels.

In this way it can support the Zigbee Router role, concurrently with a Thread Router (REED) role, even if these networks run on different RF channels. Or alternatively, it can be used to serve a Zigbee coordinator for up to 3 different ZigBee networks at the same time, each network running on a potentially different RF channel.

## 5.3 Bluetooth Communications

The QPG6105 implements the Bluetooth Low Energy (LE) Controller functionality, including PHY, Link Layer and Host Controller Interface (HCI) according the Bluetooth Core Specification v 5.3 for Bluetooth Low Energy. When combined with a Bluetooth Low Energy protocol stack (see chapter 8), it supports all GATT-based profiles and services, and it can operate as a Broadcaster, Observer, Central and Peripheral device.

#### 5.3.1 2.4 GHz Bluetooth Low Energy PHY Layer

The QPG6105 implements the Bluetooth LE PHY layer, supporting all the (40) Bluetooth defined frequency channels in the 2.4 GHz ISM license-free frequency band.

The Bluetooth LE Controller supports the following bit-rates:

Basic data rate: 1 Mbit/s, Enhanced data rate: 2 Mbit/s.

Note: The QPG6105 does not support the Long Range Coded PHY and Isochronous Channels (LE Audio).

### 5.3.2 Real-Time Bluetooth Low Energy Link Layer

The Real-Time Link Layer implements the real-time functions of the Bluetooth LE Link Layer (LL) protocol for the Advertising-, Scanning, Initiating and Connection States. Multi-state operation is supported: a multi-level priority mechanism ensures appropriate scheduling of Advertising, Scanning, Initiating and Connection- events.

In the Connection State, the Real-Time Link Layer maintains the LE Asynchronous Connection-oriented Logical (LE ACL) transport on master and/or slave connections, allowing transfer of control (LE-C) and user (LE-U) data. High-throughput applications are supported via a dedicated queue per (LE ACL) connection, thus ensuring efficient filling of Connection Events.

The QPG6105 supports the maximum PDU payload size of 255 bytes (including MIC), which is the maximum PDU payload size allowed by the Bluetooth Core Specification.

The QPG6105 supports the Link Layer Privacy and Advertising Extensions as defined in the Bluetooth Core Specification v 5.3.

#### 5.3.3 Full Connection Utilization

The QPG6105 has been optimized for audio streaming over Bluetooth Low Energy with a full Bluetooth connection utilization under high CPU load conditions. This implies that the system can fill the complete connection with Bluetooth packets allowing to achieve the maximal bandwidth of the connection, even when the CPU is processing audio (decimation, equalizing, compressing), under a large variety of Bluetooth connection configurations (normal data and high data rate, short and long connection intervals, short and long Bluetooth packets).

# 5.4 Multi-Stack Support

The QPG6105 can support multiple protocol stacks. Multiple IEEE 802.15.4 based stacks (Zigbee, Thread, proprietary) can interface simultaneously with the QPG6105 MAC API through a MAC Dispatcher, while the Bluetooth Low Energy Stack can interface with the QPG6105 at the Host Controller Interface (HCI) level at the same time.

# 5.5 HW-Accelerated Dynamic Multi-Protocol Support

The QPG6105 has HW support to seamlessly interleave Bluetooth Low Energy communications (advertisements and Bluetooth connections) with IEEE 802.15.4 communications. The Dynamic Multi-Protocol Support lets the IEEE 802.15.4 MAC autonomously schedule and interleave IEEE 802.15.4 traffic to ensure that Bluetooth connection traffic is maintained without any connection drops.

For use cases where the airtime needs to be divided differently between Bluetooth and IEEE 802.15.4 data transfers, the following additional modes are supported:

- Best effort mode, for non-real-time (bulk) Bluetooth data transfers, where the Bluetooth LE controller frees up airtime in the connection when an IEEE 802.15.4 data packet is queued.

- Controlled bandwidth mode, for real-time (streaming) Bluetooth data transfers, where the Bluetooth LE controller reserves a portion of the connection for IEEE 802.15.4 communication.

This feature can be combined with Multi-Channel Support to support three IEEE 802.15.4 stacks, while simultaneously acting as a Bluetooth Low Energy peripheral and maintain a Bluetooth connection with a smartphone.

# **5.6** ConcurrentConnect™ Multi-Radio Capability

The QPG6105 can concurrently listen to one IEEE 802.15.4 RF channel, and one Bluetooth advertisement channel.

In this way it can combine a Zigbee Router role with Bluetooth Low Energy Central/Observer role. Another example would be the combination of a (Matter over) Thread Router role with a Bluetooth Low Energy Mesh Node.

Note: ConcurrentConnect listening mode applies to Bluetooth **advertisement** channels and hence to the 1 Mbit/s data rate. It does not apply to 2 Mbit/s data rate as that is not used for advertisement channels.

# 5.7 Advanced Security Engine

The QPG6105 is equipped with a low power Advanced Security Engine that can work independently from the PHY and MAC.

The Advanced Security Engine supports:

- Hardware accelerated AES and CCM/CCM\* encryption and decryption with 128, 192 and 256-bit keys

Note: For Zigbee and Thread the 128-bit CCM\* is used. For Bluetooth Low Energy the 128-bit CCM is used.

- Hashing: SHA-128, SHA-2 (SHA-256, SHA-512)

- Public Key Cryptography: Elliptic Curve

- o Support for ECDSA, ECDH, P256, Curve25519, J-Pake, ECMQV, EdDSA, etc.

- Cryptographic Random Number Generation, designed for compliance with NIST-800-90B

## 5.8 Built-in Security Features

The QPG6105 has the following built-in security features:

- Secure boot from ROM

- Secure OTA upgrade support

- Secure Debug provisions

- Secure Key Storage

- Secure Key Load

- o Secure Symmetric Key Generation

- o Secure Public/Private Key Pair Generation

- Secure Identity support

# 5.9 Packet Input Output (PIO)

The Packet Input Output (PIO) controls the exchange of primitives and packets between the microcontroller and the 802.15.4 Real-Time MAC, as well as the exchange of (LE-C and LE-U) packets between the microcontroller and the Bluetooth LE Real-Time Link Layer. Information about a packet or other primitive parameters is stored in Packet Buffer Memory (PBM), a reserved region of the RAM that can hold information for up to 32 packets. The number of packets is software configurable; the application needs to make sure there are sufficient PBMs available to meet the requirements. These PBM entries are shared between the 802.15.4 MAC (RX & TX) and Bluetooth (RX & TX) functions.

# **5.10 Memory Architecture**

The QPG6105 contains:

**128 Kbyte RAM**: Low Leakage Random Access Memory (RAM), for packet buffering and run-time data. This is split in:

32 Kbyte is System RAM, accessible to the internal microcontroller and other functional blocks, and 96 Kbyte is MCU RAM, accessible to the internal microcontroller only.

The contents of the RAM can be retained (or partially retained) during standby modes but is cleared when a Power-On-Reset (POR) occurs.

| Table | 1: RAN | I Retention | Options |

|-------|--------|-------------|---------|

|-------|--------|-------------|---------|

| RAM Block<br>Size | RAM Block<br>Type | Total RAM<br>Retained | Retained RAM Type    |

|-------------------|-------------------|-----------------------|----------------------|

| 8 Kbyte           | System RAM        | 8 Kbyte               | System RAM           |

| 24 Kbyte          | System RAM        | 32 Kbyte              | System RAM           |

| 32 Kbyte          | MCU RAM           | 64 Kbyte              | System RAM + MCU RAM |

| 32 Kbyte          | MCU RAM           | 96 Kbyte              | System RAM + MCU RAM |

| 32 Kbyte          | MCU RAM           | 128 Kbyte             | System RAM + MCU RAM |

**1 Mbyte Flash**: Flash memory, for program storage, calibration data and non-volatile storage of critical runtime data (e.g. pairing information and frame counters). The contents are retained under all circumstances (power-on-reset, standby).

**ROM**: Integrated patchable ROM (256 Kbyte) to provide off-load functionality to significantly reduce the Flash code footprint. Items included in ROM are:

- Security Primitives

- o Core SW modules and functions: Scheduler; HAL; Bluetooth LE Controller; IEEE 802.15.4 MAC

- Matter-specific offload: Bluetooth LE Host; NVM SW module

**DMA Engine :** The QPG6105 has an 8-channel DMA Engine that relieves the microcontroller from transferring data internally between RAM and peripherals.

### **5.11 Internal Microcontroller**

The internal microcontroller allows the QPG6105 to operate as a standalone system. It is a high performance 32-bit Arm Cortex-M4 processor with DSP functionality, optimized for low power consumption, performance, and code size.

It runs at up to 64 MHz clock speed, and can execute code from Flash as well as from RAM, with zero wait states.

**Table 2: Memory Access Speeds**

| Arm clock | MCU RAM access | System RAM access | ROM access | Flash Memory access                          |

|-----------|----------------|-------------------|------------|----------------------------------------------|

| 32 MHz    | 32 MHz         | 32 MHz            | 32 MHz     | 32 MHz for linear code;<br>16 MHz worst case |

| 64 MHz    | 64 MHz         | 32 MHz            | 32 MHz     | 42 MHz for linear code;<br>16 MHz worst case |

## 5.12 Peripherals

The QPG6105 features a set of peripherals and allows configuration of the mapping between the IO signals needed by the peripherals and the available IO pins.

#### 5.12.1 IO Pins

The QPG6105 features many IO pins that can be configured to predefined functional signals; see the Pin Assignments in chapter 11:

- 17 programmable General Purpose IO (GPIO) lines, plus

- 4 programmable Analog IO (ANIO) or GPIO lines (of which 2 input only), plus

- 2 pins for the optional 32 KiHz crystal IO can alternatively be used as GPIO (input only) lines.

The whole pin configuration with associated settings is retained when going to standby.

#### 5.12.1.1 GPIO

The QPG6105 features programmable GPIO lines that are mapped individually to functional signals, as specified in the Pin Assignments in chapter 11 (Table 30), with following settings:

**Pin pull-up/down settings**: Except for GPIO19 and GPIO20, the GPIO pins can be individually weakly pulled up or weakly pulled down during active as well as standby states.

Except for GPIO19, GPIO20, GPIO21 and GPIO22, the GPIO pins can be individually configured for bus-keeper.

Unless specified otherwise, at power-up/reset all GPIO pins are default set in floating mode.

**Drive strength**: The drive strength of the GPIO output pins can be configured per group of 4 IO's (GPIO0 ... GPIO3, GPIO4 ... GPIO7, etc.; see also Table 30) to 4.5, 9, 13.5 or 18 mA.

**Wake up**: All GPIO pins can be configured as **wake-up** pin. Each of these can be configured to trigger a wake-up event on a rising edge, on a falling edge or on both edges seen on the pin.

#### 5.12.1.2 ANIO

The QPG6105 features up to 4 ANIO lines for inputs to the ADC. ANIO0 and ANIO1 are the preferred ones as they are protected from potential interference by output signals. ANIO0 and ANIO1 can also be used for differential measurements.

#### 5.12.2 **UARTs**

The QPG6105 contains two Universal Asynchronous Receiver and Transmitters (UARTs) for interfacing with additional peripheral devices and/or for terminal logging during (software) development. The UARTs support:

- Full-duplex operation.

- Baud rates from 488 Bd to 2 MBd.

- Serial frames with 5, 6, 7, 8 or 9 data bits and 1 or 2 stop bits, with framing error detection.

- · Odd or even parity generation and checking.

- Buffer overflow detection.

- False start bit detection and digital low pass filter for robustness against noise.

- Separate interrupts on TX Complete, TX Data Register Empty and RX Complete.

- Configurable pin mappings; i.e. a RX pin and a TX pin can be made available on the pin-out.

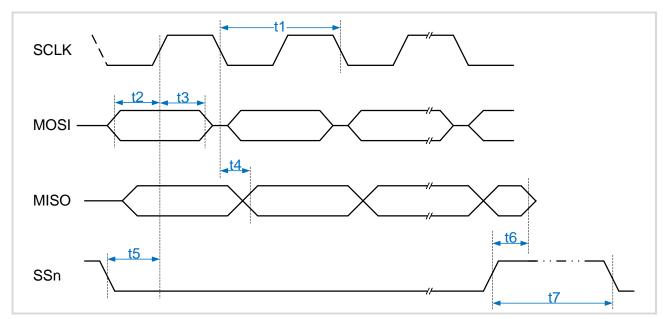

#### 5.12.3 SPI Master

The QPG6105 contains a Serial Peripheral Interface (SPI) for interfacing with additional peripheral devices. This SPI Master supports:

- Full-duplex synchronous transfers on three lines (MISO, MOSI, SCLK).

- Programmable clock polarity and phase, supports SPI mode 0, 1, 2 and 3.

- Programmable data order with MSb-first or LSb-first shifting.

- High speed clock generator supporting clock speeds up to 32 MHz.

- 4-bit to 16-bit transfer frame format selection.

- Three separate interrupts on TX Complete, TX Data Register Empty and RX Complete.

#### **5.12.4** SPI Slave

The QPG6105 contains an SPI Slave interface. This SPI Slave supports:

- SPI mode 0

- SPI clock frequencies up to 16 MHz

- Limited to byte-based operation

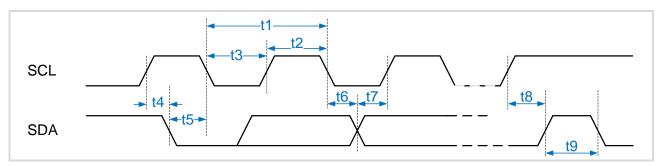

#### 5.12.5 I<sup>2</sup>C Master

The QPG6105 contains an I<sup>2</sup>C (Inter-Integrated Circuit) Master interface, also referred to as Two-Wire Interface (TWI), for interfacing with additional peripheral devices. This I<sup>2</sup>C Master supports:

- Standard mode and Fast mode

- Short (7-bit) and long (10-bit) addresses

- General call address (0x00)

- Clock stretching

#### 5.12.6 I<sup>2</sup>C Slave

The QPG6105 contains an I<sup>2</sup>C Slave interface. This I<sup>2</sup>C Slave supports:

- Standard mode and Fast mode

- Short (7-bit) and long (10-bit) addresses

- Configurable Slave Address

- General call address (0x00)

#### 5.12.7 I<sup>2</sup>S Master/Slave

The QPG6105 contains an I<sup>2</sup>S (Inter-IC Sound) Master/Slave interface for interfacing with digital audio devices. This I<sup>2</sup>S Master/Slave supports:

- Full duplex transfers

- Configurable word length

- · Left justified. Right justified mode can be emulated

- Double buffered, DMA capable

- Master clock frequency selectable from 62.5 kHz up to 8 MHz

- External Slave clock input supporting speeds up to 4 MHz

## 5.12.8 IR Signal Generator

The QPG6105 has an InfraRed (IR) signal generator. The IR signal generator supports a wide range of common IR protocols.

The IR generator supports multiple modulation modes:

Pattern based: input is a pattern of 0's and 1's in RAM.

Time based: input is a sequence of ON and OFF times.

Event based: modulation is controlled by scheduled actions.

## **5.12.9 LED Signal Generator**

The QPG6105 supports up to 4 signaling LEDs, with configurable function and events. The LED signal generator supports:

- 8-bit Pulse-Width Modulation (PWM)

- Fade-in/Fade-out

- · Duty cycling to adjust brightness and save power

#### 5.12.10 PDM Microphone Interface

The QPG6105 contains a Pulse-Density Modulation (PDM) MEMS Microphone Interface, that supports:

- A Clock and Data pin for interfacing with a PDM MEMS microphone

- Optionally Capturing Data on the Rising and Falling Edge of the Clock for Stereo operations.

- Frequency of Clock signal: 2 MHz.

- HW CIC Decimation filter with programmable decimation factor (R=1...64) that converts 1-bit input samples to 16-bit output samples. HW CIC output can be connected to DMA, to allow this processing chain to be extended with further decimation, equalization, volume control and compression using the Cortex M4 DSP routines.

## **5.12.11 PWM Engine**

The QPG6105 contains a Pulse-Width Modulation (PWM) engine, for e.g. the backlight of a display or for a speaker output, that supports:

- 16-bits real-time timer. (Note that the Event Scheduler contains a timer with a much longer time base; see section 5.13 below)

- 16-bit PWM

- Configuration of the modulation parameters

- Support for 8 PWM outputs.

#### 5.12.12 Generic Timer

The Generic Timer supports:

- 16-bits real-time timer. (Note that the Event Scheduler contains a timer with a much longer time base; see section 5.13 below)

- The option to take a timestamp whenever a selected input pin changes state. This can typically be used for IR learning purposes.

- Support for 4 timestamp inputs.

- o Input pin selection.

- o Hysteresis capable preprocessing.

## **5.12.13 Watchdog**

The QPG6105 contains a Watchdog timer that serves to detect and resolve software failures and to trigger an interrupt, an internal microcontroller reset or a system reset when the timer reaches a certain timeout value. Timeout values are software configurable: 16-bit values in 16 µs resolution.

## 5.12.14 Intelligent Sensor Hub

The QPG6105 supports an Intelligent Sensor Hub mode for ultra-short measurement cycles for battery operated sensors, ensuring minimal battery usage for these measurements. Upon wake up from standby mode (see also section 5.13 below) measurements and calculations can be performed running on the internal system clock to determine quickly whether the system should be fully woken up (e.g. for radio transmission, requiring the 32 MHz crystal oscillator) or can go back to standby. This whole cycle is intended to take less than 100 µs.

Through software configuration, all analog input channels (ANIO, see section 5.12.1) can be connected to the ADC and to the Comparator. The battery and temperature monitor signals can also be connected to the ADC.

#### 5.12.14.1 ADC

The QPG6105 has an integrated ADC module that can be used to monitor external analog signals via the ANIO pins (see section 5.12.1.2) as well as the power supply level and temperature.

- ANIO0 and ANIO1 can be used for differential measurements.

- The ADC runs on 4 MHz clock speed. A total of 16 cycles are needed to obtain a conversion result.

Table 22 in section 6.11 provides the ADC's accuracy and other characteristics.

#### 5.12.14.2 Battery / Temperature Monitor

The ADC can be configured by software to monitor the power supply level and/or temperature internally; no external components are required. The power supply level and temperature are measured separate from the ANIO pins.

Figure 4: Battery / Temperature Monitor

#### **5.12.14.3** Comparator

The QPG6105 features a low power comparator that can be used to trigger events to wake up the chip and/or trigger an action. The low power analog comparator can be connected to analog input(s). It supports 4 slots, allowing for time multiplexed measurements on different channels and with different threshold configurations. The comparator can be configured to combine such measurements to 'windowed' events (i.e. value is between two configurable levels).

## 5.12.15 Clock Output

The QPG6105 can provide a clock to peripheral devices (CLK\_OUT). The clock frequency is derived from the 32 MHz crystal oscillator system clock. It can be configured for:

- 1, 2, 4, or 8 MHz clock with 50% duty cycle

- 16 MHz pulse blanked clock.

## **5.13 Timing and Control**

The QPG6105 is designed to work in an environment where low power consumption is very important. To achieve the low power consumption in between receive and transmission cycles, the QPG6105 can be put in a standby (or sleep) state.

Following are the reasons for the QPG6105 to wake up:

- An event is detected on one of the IO lines (falling edge or rising edge).

- The voltage of an analog IO goes over or under a configurable threshold.

- It is time for a scheduled action.

The QPG6105 features a highly accurate and adaptive timing engine. The time base spans up to 30 minutes with a 1 µs resolution and can be maintained during the standby modes. It can be used to autonomously and periodically schedule actions listed below in a just-in-time manner, improving the overall energy consumption of the system:

- Transmission of a packet from a TX queue.

- Enabling/disabling the receiver.

- Switch on/off IR modulation

- Trigger ADC measurement cycle

- Trigger analog measurements

- Interrupt and wake up the microcontroller.

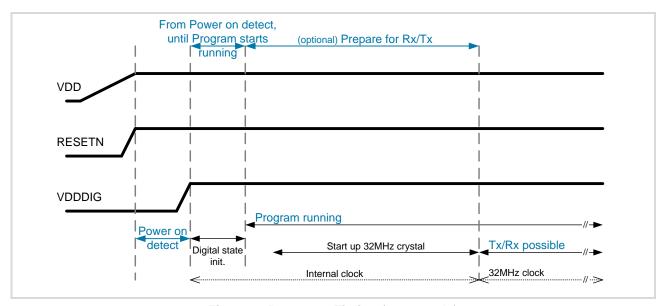

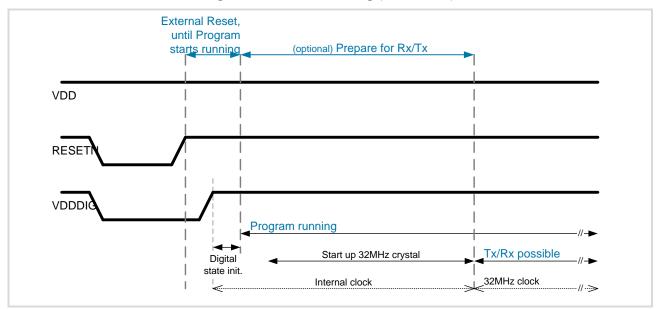

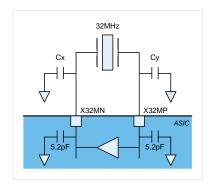

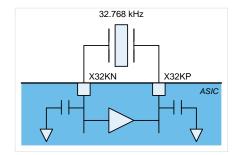

## 5.13.1 Oscillator Settings

The QPG6105 includes the following oscillators:

- **32 MHz crystal oscillator**, based on the required external 32 MHz crystal. This is used as main system clock and reference frequency to obtain the desired RF performance.

- Internal system clock. This internal clock generator is used for fast start-up and initial processing. Its frequency

is close to 32 MHz but its frequency accuracy is insufficient for RF performance. It can also be used for the Intelligent Sensor Hub, enabling minimum wake-up time to perform

analog measurements.

32 kHz LjRC oscillator. This internal low jitter RC oscillator is designed to support applications needing an

accurate time-base during standby, effectively removing the need for a 32 KiHz oscillator with external crystal. High accuracy is obtained through regular calibration of the LjRC

oscillator using the 32 MHz crystal reference clock.

Optional **32 KiHz crystal oscillator**, based on the optional external 32 KiHz crystal. This oscillator can be used when more accurate timing during standby is needed. As a side effect of the more accurate timing, the power consumption can be improved as well for applications that implement synchronized wake up events (i.e. Bluetooth LE) as the more accurate timing results in a smaller guard band and more time spent in sleep mode.

## 5.13.2 Standby Modes

The QPG6105 supports the following standby modes (see section 6.3 Table 5 for the power consumption):

- **XT Standby** mode: A low power mode that requires no reconfiguration (partial or full state retention). The time base for the Event Scheduler is delivered by the 32 MHz crystal oscillator.

- **RC Standby** mode: A low power mode that requires no reconfiguration (partial or full state retention). The time base for the Event Scheduler is delivered by the internal 32 kHz LjRC oscillator.

- **32KiHz Standby** mode: An optional low power mode that requires no reconfiguration (partial or full state retention). The time base for the Event Scheduler is delivered by the oscillator based on the optional 32 KiHz crystal.

In all standby modes, the QPG6105 can be programmed to also be woken up by an external event.

Note: During RC Standby and 32 KiHz Standby modes various amounts of RAM can be retained (see section 5.10). RC Standby mode and 32 KiHz Standby mode are only supported up to 85°C. Applications up to 125°C should use XT Standby mode.

## **5.14 Power Management**

The QPG6105's integrated power management system includes a Global Low Dropout Regulator (GLDO). This generates an internal 1.8 V power supply rail that is used to supply separate local LDO regulators feeding RF/analog and digital blocks. The local LDOs used to supply RF/analog blocks are specially designed to have high power supply rejection ratio (PSRR) to suppress supply ripples.

## 5.14.1 Low Voltage Behavior

The QPG6105 contains following features that can be combined to implement the desired low voltage behavior:

VDD Brown-out Interrupt: Interrupt that can be software configured to trigger when VDD drops below the VDD Brown-out threshold while being active. This interrupt can be used to trigger the software to disable the radio and go into standby mode. A higher value gives the application more time for state cleanup. The VDD Brown-out threshold is software configurable: 1.80, 1.85, 1.90 or 1.95 V; default value is 1.80 V.

The VDD Brown-out detector is enabled and configured by software. In case that the Brown-out detector is not enabled, the Cut-Off detector is used to ensure reliable low voltage behavior.

**VMT**

: Voltage Minimum Threshold (VMT), under which the chip will not wake up from standby mode. VMT is software configurable; range = 1.6 ... 3.1 V; default value is 1.65 V.

VMT crossing detection time is software configurable; default is 125 µs.

Power On Reset voltage level at which the chip will start up is determined by the VMT level; this is guaranteed to be  $\leq 1.8 \text{ V}$  at POR.

Cut-Off

: A VDD threshold under which all functions are disabled, and current consumption is strictly limited. The Cut-Off threshold changes with the configured Brown-out threshold as follows:

| Brown-out threshold | Cut-Off threshold |

|---------------------|-------------------|

| 1.80 V (default)    | 1.65 V            |

| 1.85 V              | 1.69 V            |

| 1.90 V              | 1.72 V            |

| 1.95 V              | 1.76 V            |

**POR Circuit Timing**: The Power On Reset circuit resets the chip before the VDD voltage reaches the minimal operating voltage. The chip embeds a Power On Reset circuit with internal and external triggers.

| Trigger Type                   | Trigger condition (Typ)     | Response time (Typ) |

|--------------------------------|-----------------------------|---------------------|

| Internal (on chip VDD monitor) | VDD << 1 V                  | 1 ms                |

| External (RESETn input)        | V <sub>resetn</sub> < ½ VDD | <10 ns              |

Note: The internal reset trigger circuit samples VDD, the circuit behaves similar to a sample-based circuit at 1 kHz.

The external reset trigger uses an asynchronous (direct) input.

## **6 Electrical Characteristics**

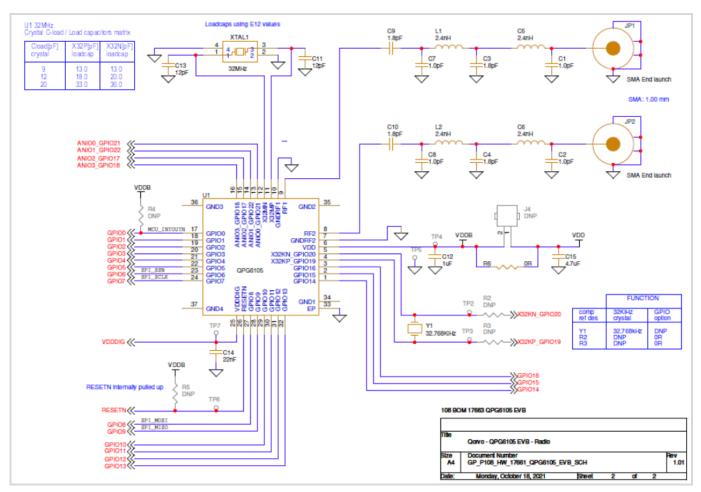

The QPG6105 characteristics are determined in a circuit like shown in Figure 5 below.

Note: The circuit shown is an evaluation circuit for measurement purposes and <u>not</u> a reference design.

**Figure 5: Parameter Evaluation Circuit**

- Transmit as well as receive behavior is measured in accordance with the IEEE 802.15.4 specification and the Bluetooth Test Specification (RF-PHY.TS.5.0.1).

- All parameters are measured at VDD = 3.0 V and T<sub>A</sub> = 25 °C, unless otherwise specified.

- IEEE 802.15.4 channel rejection is measured with the QPG6105 reference design system as interferer.

# 6.1 Absolute Maximum Ratings

**Table 3: Absolute Maximum Ratings**

| Symbol                                                                    | Parameter                                               |                | Value                           | Unit |               |   |

|---------------------------------------------------------------------------|---------------------------------------------------------|----------------|---------------------------------|------|---------------|---|

| VDD                                                                       | Supply Input Voltage                                    |                | -0.3 to +3.6                    | V    |               |   |

| All Digital pins, including<br>"Analog or Digital" pins<br>(see Table 29) | Digital IO Voltage                                      |                | -0.3 to VDD+0.3 $(Max = +3.6)$  | V    |               |   |

| All Analog pins<br>(see Table 29)                                         | Analog IO Voltage                                       |                | -0.3 to +1.32                   | V    |               |   |

| VDDDIG                                                                    | Decoupling Voltage                                      |                | Decoupling Voltage              |      | -0.3 to +1.32 | V |

| RF1, RF2                                                                  | RF IO Voltage                                           |                | -0.3 to +0.3                    | V    |               |   |

| P <sub>MAX</sub>                                                          | Input RF level                                          | Input RF level |                                 | dBm  |               |   |

| TJ                                                                        | Junction Temperature                                    | )              | +125                            | °C   |               |   |

| T <sub>stg</sub>                                                          | Storage Temperature                                     |                | -50 to +150                     | °C   |               |   |

| T <sub>sol</sub>                                                          | Reflow Soldering Tem                                    | nperature      | +260 (10 s max.)                | °C   |               |   |

|                                                                           | ESD HBM                                                 |                | Class 1C                        |      |               |   |

|                                                                           | (ANSI/ESDA/JEDEC<br>JS-001-2017                         | RF pins:       | (1000 V to < 2000 V)            |      |               |   |

|                                                                           | Human Body Model)                                       | non-RF pins:   | (2000 V to < 4000 V)            |      |               |   |

|                                                                           | ESD CDM<br>(ANSI/ESDA/JEDEC JS<br>Charged Device Model) | -002-2018      | Class C2a<br>(500 V to < 750 V) |      |               |   |

# **6.2 Recommended Operating Conditions**

**Table 4: Recommended Operating Conditions**

| Symbol           | Parameter                               | Conditions                                |             | Min     | Тур | Max  | Unit |

|------------------|-----------------------------------------|-------------------------------------------|-------------|---------|-----|------|------|

| VDD              | Power Supply Voltage                    |                                           |             | 1.8     | 3.0 | 3.6  | V    |

| T <sub>A</sub>   | Ambient Temperature                     |                                           |             | -40     | +25 | +125 | °C   |

| F <sub>ref</sub> | Reference Crystal Oscillation Frequency |                                           |             |         | 32  |      | MHz  |

|                  |                                         |                                           | VDD = 1.8 V |         |     | 0.6  | V    |

| $V_{IL}$         | Input Low Voltage for all GPIO lines    | Logical value (functional)                | VDD = 3.0 V |         |     | 1.0  |      |

|                  |                                         | (runctional)                              | VDD = 3.6 V |         |     | 1.3  |      |

|                  |                                         | Analogue value (prevents leakag           | e current)  |         |     | 0.25 | V    |

|                  |                                         |                                           | VDD = 1.8 V | 1.0     |     |      | V    |

| $V_{IH}$         | Input High Voltage for all GPIO lines   | Logical value (functional)                | VDD = 3.0 V | 1.6     |     |      |      |

|                  | iiies                                   | VDD = 3                                   |             | 2.0     |     |      |      |

|                  |                                         | Analogue value (prevents leakage current) |             | VDD – 0 | .25 |      | V    |

| Symbol                                | Parameter                                                                       | Cond     | itions                           |                      | Min         | Тур        | Max      | Unit |

|---------------------------------------|---------------------------------------------------------------------------------|----------|----------------------------------|----------------------|-------------|------------|----------|------|

|                                       |                                                                                 | VDD      | Drive<br>Strength <sup>(*)</sup> | l <sub>OL</sub> (**) |             |            |          |      |

|                                       |                                                                                 |          | 4.5 mA                           | 3 mA                 |             | 0.4        | 0.6      |      |

| Output Low Voltage for all GPIO lines | Output Low Voltage for                                                          | 4.0.1/   | 9 mA                             | 7 mA                 |             | 0.4        | 0.6      |      |

|                                       |                                                                                 | 1.8 V    | 13.5 mA                          | 11 mA                |             | 0.5        | 0.6      | V    |

|                                       |                                                                                 |          | 18 mA                            | 15 mA                |             | 0.5        | 0.6      |      |

|                                       |                                                                                 |          | 4.5 mA                           | 4.5 mA               |             | 0.25       | 0.40     |      |

|                                       |                                                                                 | 201/     | 9 mA                             | 9 mA                 |             | 0.25       | 0.40     | \ /  |

|                                       |                                                                                 | 3.0 V    | 13.5 mA                          | 13.5 mA              |             | 0.30       | 0.45     | V    |

|                                       |                                                                                 |          | 18 mA                            | 18 mA                |             | 0.30       | 0.45     |      |

|                                       |                                                                                 |          | 4.5 mA                           | 4.5 mA               |             | 0.20       | 0.35     |      |

|                                       |                                                                                 | 3.6 V    | 9 mA                             | 9 mA                 |             | 0.20       | 0.35     | V    |

|                                       |                                                                                 | 3.6 V    | 13.5 mA                          | 13.5 mA              |             | 0.25       | 0.40     | V    |

|                                       |                                                                                 | 18 mA    | 18 mA                            |                      | 0.25        | 0.40       |          |      |

|                                       |                                                                                 | VDD      | Drive<br>Strength <sup>(*)</sup> | I <sub>OH</sub> (**) |             |            |          |      |

|                                       |                                                                                 | 1.8 V    | 4.5 mA                           | -4.5 mA              | 1.1         | 1.3        |          | V    |

|                                       |                                                                                 |          | 9 mA                             | -9 mA                | 1.1         | 1.3        |          |      |

|                                       |                                                                                 |          | 13.5 mA                          | -13.5 mA             | 1.0         | 1.2        |          |      |

|                                       |                                                                                 |          | 18 mA                            | -18 mA               | 1.0         | 1.2        |          |      |

|                                       | Output High Voltage for                                                         | 3.0 V    | 4.5 mA                           | -4.5 mA              | 2.45        | 2.7        |          | V    |

| ОН                                    | all GPIO lines                                                                  |          | 9 mA                             | -9 mA                | 2.45        | 2.7        |          |      |

|                                       |                                                                                 |          | 13.5 mA                          | -13.5 mA             | 2.35        | 2.6        |          | V    |

|                                       |                                                                                 |          | 18 mA                            | -18 mA               | 2.35        | 2.6        |          |      |

|                                       |                                                                                 |          | 4.5 mA                           | -4.5 mA              | 3.1         | 3.4        |          |      |

|                                       |                                                                                 | 3.6 V    | 9 mA                             | -9 mA                | 3.1         | 3.4        |          | V    |

|                                       |                                                                                 | 3.0 V    | 13.5 mA                          | -13.5 mA             | 3.0         | 3.3        |          | V    |

|                                       |                                                                                 |          | 18 mA                            | -18 mA               | 3.0         | 3.3        |          |      |

| notes:                                | * Refer to section 5.12.1. ** I <sub>OL</sub> / I <sub>OH</sub> : positive valu |          |                                  | negative valu        | e: pin is s | sourcing o | current. |      |

| рН                                    | Total sourced current for output lines combined                                 | all GPIO |                                  |                      |             |            | 100      | mA   |

| INT                                   | Pulse width for GPIO inte                                                       | rrupts   |                                  |                      | 250         |            |          | ns   |

# **6.3 Current Consumption**

**Table 5: Current Consumption - Common**

| Symbol  | Parameter                                                                                        |                                       | Conditions                        | Min | Тур  | Max | Unit |

|---------|--------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------|-----|------|-----|------|

| lidle   | Idle Modes                                                                                       |                                       | Arm asleep                        |     | 2.0  |     |      |

|         |                                                                                                  |                                       | Arm running from RAM              |     |      |     |      |

|         |                                                                                                  |                                       | @ 32 MHz                          |     | 3.6  |     |      |

|         | (runnina Corel                                                                                   | Mark reference program.)              | @ 64 MHz                          |     | 5.0  |     | mΑ   |

| , ,     | al XTAL 32 MHz running)                                                                          | Arm rupping from Floob                |                                   | 5.5 |      |     |      |

|         |                                                                                                  |                                       | @ 64 MHz                          |     | 6.9  |     |      |

| standby | Standby Modes                                                                                    | RC Standby mode<br>8 Kbyte RAM ret    |                                   |     | 0.9  |     |      |

|         |                                                                                                  | 32 Kbyte RAM retained                 |                                   |     | 1.3  |     |      |

|         |                                                                                                  | 64 Kbyte RAM retained                 |                                   |     | 2.3  |     |      |

|         |                                                                                                  | 96 Kbyte RAM re                       |                                   | 3.1 |      |     |      |

|         |                                                                                                  | 128 Kbyte RAM                         |                                   | 4.0 |      |     |      |

|         |                                                                                                  | 32 KiHz Standby n<br>8 Kbyte RAM ret  |                                   |     | 1.6  |     |      |

|         |                                                                                                  | 32 Kbyte RAM retained                 |                                   |     | 2.0  |     | μΑ   |

|         |                                                                                                  | 64 Kbyte RAM retained                 |                                   |     | 3.0  |     |      |

|         | 96 Kbyte RAM<br>128 Kbyte RAM                                                                    |                                       | etained                           |     | 3.8  |     |      |

|         |                                                                                                  |                                       | retained                          |     | 4.7  |     |      |

|         | (Current consumption depends on crysta specification and load capacitance, see section 6.9 below |                                       | XT Standby mode                   |     | 765  |     |      |

|         | Current increase by activated comparator (measurement frequency dependent)                       |                                       | Measurement frequency<br>= 32 kHz |     | 0.23 |     |      |

| eset    | Reset Mode                                                                                       | · · · · · · · · · · · · · · · · · · · |                                   |     | 50   |     | μΑ   |

note: \* RC Standby mode and 32 KiHz Standby mode are only supported up to 85°C. Applications up to 125°C should use XT Standby mode.

Table 6: Current Consumption - IEEE 802.15.4

| Symbol  | Parameter                                   | Conditions                                                 | Min | Тур  | Max | Unit |  |

|---------|---------------------------------------------|------------------------------------------------------------|-----|------|-----|------|--|

| lactive | Active Modes<br>(Operating in IEEE 802.15.4 | RX listening*, single antenna                              |     | 5.6  |     |      |  |

| cnar    | channel 20)                                 | RX listening,<br>single channel, with<br>antenna diversity |     | 7.4  |     |      |  |

|         |                                             | RX listening,<br>multi-channel, with<br>antenna diversity  |     | 11.5 |     | mA   |  |

|         |                                             | RX receiving packet                                        |     | 10.2 |     |      |  |

|         |                                             | TX @ 0 dBm                                                 |     | 16.7 |     |      |  |

|         |                                             | TX @ 7 dBm, low power mode                                 |     | 26.4 |     |      |  |

|         |                                             | TX @ 10 dBm, high power mode                               |     | 38.8 |     |      |  |

| Note:   | * "RX listening" is define                  | d as receive mode during preamble hunt                     |     |      |     | 1    |  |

**Table 7: Current Consumption - Bluetooth Low Energy**

| Parameter | Conditions                      |                                            | Min                                                                                                                                                      | Тур                                                                                                                                                           | Max                                                                                                                                                                              | Unit                                                                                                                                                                             |    |

|-----------|---------------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Active    |                                 | RX listening* 1 Mbit/s                     |                                                                                                                                                          | 10.4                                                                                                                                                          |                                                                                                                                                                                  |                                                                                                                                                                                  |    |

| Modes     |                                 | RX listening 2 Mbit/s                      |                                                                                                                                                          | 10.7                                                                                                                                                          |                                                                                                                                                                                  |                                                                                                                                                                                  |    |

|           |                                 | RX receiving packet (1 Mbit/s or 2 Mbit/s) |                                                                                                                                                          | 12.4                                                                                                                                                          |                                                                                                                                                                                  |                                                                                                                                                                                  |    |

|           |                                 |                                            | TX @ 0 dBm                                                                                                                                               |                                                                                                                                                               | 16.7                                                                                                                                                                             | mA                                                                                                                                                                               | mA |

|           |                                 | TX @ 7 dBm,<br>low power mode              |                                                                                                                                                          | 26.4                                                                                                                                                          |                                                                                                                                                                                  |                                                                                                                                                                                  |    |

|           | TX @ 10 dBm,<br>high power mode |                                            | 38.8                                                                                                                                                     |                                                                                                                                                               |                                                                                                                                                                                  |                                                                                                                                                                                  |    |

| ,         | Active                          | Active                                     | Active Modes  RX listening* 1 Mbit/s RX listening 2 Mbit/s RX receiving packet (1 Mbit/s or 2 Mbit/s) TX @ 0 dBm TX @ 7 dBm, low power mode TX @ 10 dBm, | Active Modes  RX listening* 1 Mbit/s  RX listening 2 Mbit/s  RX receiving packet (1 Mbit/s or 2 Mbit/s)  TX @ 0 dBm  TX @ 7 dBm, low power mode  TX @ 10 dBm, | Active Modes RX listening* 1 Mbit/s 10.4 RX listening 2 Mbit/s 10.7 RX receiving packet (1 Mbit/s or 2 Mbit/s) TX @ 0 dBm 16.7 TX @ 7 dBm, 26.4 low power mode TX @ 10 dBm, 38.8 | Active Modes RX listening* 1 Mbit/s 10.4 RX listening 2 Mbit/s 10.7 RX receiving packet (1 Mbit/s or 2 Mbit/s) TX @ 0 dBm 16.7 TX @ 7 dBm, 26.4 low power mode TX @ 10 dBm, 38.8 |    |

## Table 8: Current Consumption - ConcurrentConnect Mode

| Symbol | Parameter                                                               | Conditions |                                                         | Min | Тур  | Max | Unit |  |

|--------|-------------------------------------------------------------------------|------------|---------------------------------------------------------|-----|------|-----|------|--|

| active | Active Modes                                                            |            | RX listening* concurrent IEEE 802.15.4 and Bluetooth LE |     | 11.6 |     | mA   |  |

| Note:  | Note: * "RX listening" is defined as receive mode during preamble hunt. |            |                                                         |     |      |     |      |  |

# 6.4 Receiver Characteristics

**Table 9: Receiver Characteristics - Common**

| Parameter                                              | Conditions     |                   | Min  | Тур | Max | Unit    |

|--------------------------------------------------------|----------------|-------------------|------|-----|-----|---------|

| RSSI range                                             | E dD accompany | AGC activated     | -101 |     | -33 | al Duna |

| (assuming the HAL is used, see sections 5.1.3 and 8.1) | 5 dB accuracy  | AGC not activated | -101 |     | -50 | dBm     |

|                                                        | Resolution     |                   |      | 1   |     | dB      |

| LO leakage                                             | 2.4 GHz        |                   |      |     | -47 | dBm     |

|                                                        | 4.8 GHz        |                   |      |     | -47 | ubili   |

Table 10: Receiver Characteristics - IEEE 802.15.4

| Parameter                            | Conditions                                                                                                                                                     | Min  | Тур  | Max  | Unit   |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--------|

| RF channels                          | Programmable in 5 MHz steps as defined by IEEE 802.15.4                                                                                                        | 2405 |      | 2480 | MHz    |

| Bit rate                             |                                                                                                                                                                |      | 250  |      | kbit/s |

| Receiver sensitivity                 | as defined in IEEE 802.15.4 (Measured in IEEE 802.15.4 channel 20)                                                                                             |      |      |      |        |

|                                      | Single channel listening                                                                                                                                       |      | -101 |      |        |

|                                      | Multi-channel listening (signal at both antenna ports)                                                                                                         |      | -100 |      |        |

|                                      | IEEE 802.15.4 / Bluetooth LE concurrent listening Sensitivity for 2480 MHz may be up to 3 dB worse. For 2415 and 2465 MHz sensitivity may be up to 1 dB worse. |      | -98  |      | dBm    |

|                                      | Antenna Diversity Gain (refer to section 5.2.2 for the channel model)                                                                                          |      | 8    |      | dB     |

| RX carrier frequency offset range    | Sensitivity loss < 2 dB                                                                                                                                        | -200 |      | +215 | kHz    |

| Maximum receive level                | 1% PER as defined in IEEE 802.15.4                                                                                                                             | +10  |      |      | dBm    |

| IIP3                                 | RX mode, AGC enabled                                                                                                                                           |      | +1   |      | dBm    |

| P-1dB RF front-end                   | RX mode, AGC enabled                                                                                                                                           |      | -11  |      | dBm    |

| Co-Channel rejection                 | Packet in Packet collision                                                                                                                                     |      | -10  |      | dB     |

|                                      | Non-IEEE 802.15.4 Interference (noise)                                                                                                                         |      |      |      |        |

|                                      | single antenna                                                                                                                                                 |      | -3   |      | dB     |

|                                      | with antenna diversity                                                                                                                                         |      | -1   |      | ub .   |

| Adjacent channel rejection           | as defined in IEEE 802.15.4.<br>IEEE 802.15.4 interferer, +/- 5 MHz                                                                                            |      | 35   |      | dB     |

| Alternate adjacent channel rejection | as defined in IEEE 802.15.4.<br>IEEE 802.15.4 interferer, +/- 10 MHz                                                                                           |      | 47   |      | dB     |

| Far away channel rejection           | wanted signal at -82 dBm. IEEE 802.15.4 interferer, +/- 15 MHz                                                                                                 |      | 52   |      | dB     |

| Wi-Fi IEEE 802.11ax rejection        | wanted signal at -82 dBm.<br>Wi-Fi centered at +12 MHz / -13 MHz or higher offset<br>frequency                                                                 |      | 37   |      | dB     |

| Parameter                                            | Conditions                                                 | Min | Тур | Max | Unit |

|------------------------------------------------------|------------------------------------------------------------|-----|-----|-----|------|

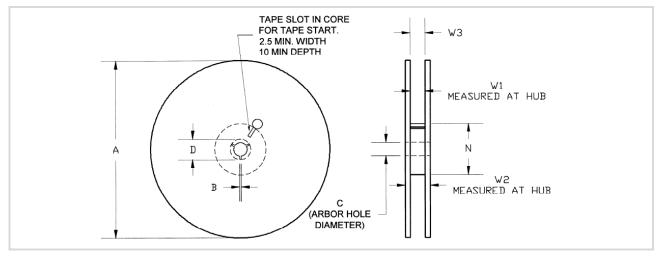

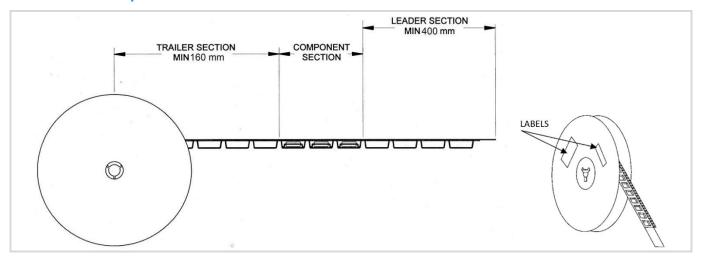

| Bluetooth rejection (fixed carrier, rejection of FSK | wanted signal at -82 dBm,<br>Bluetooth carrier at:         |     |     |     |      |